# PRODUCT/PROCESS CHANGE NOTIFICATION

PCN APM-IPC/07/2330 Notification Date 02/23/2007

2ND SOURCE ASSEMBLY LINE OF PM6685xx device (UN08 line)

& PM6680xx device (UN13 line) - VFQFPN 5X5X1 - IN UTAC THAI SUBCON

IPC - IND.& POWER CONV.

#### **Table 1. Change Identification**

| Product Identification<br>(Product Family/Commercial Product) | PM6685, PM6685TR, PM6680 & PM6680TR         |

|---------------------------------------------------------------|---------------------------------------------|

| Type of change                                                | Package assembly location change            |

| Reason for change                                             | capacity increase                           |

| Description of the change                                     | see attachment                              |

| Product Line(s) and/or Part Number(s)                         | See attached                                |

| Description of the Qualification Plan                         | See attached                                |

| Change Product Identification                                 | Traceab. assy area code inside marking "FN" |

| Manufacturing Location(s)                                     |                                             |

#### **Table 2. Change Implementation Schedule**

| Forecasted implementation date for change                                                    | 16-Feb-2007 |

|----------------------------------------------------------------------------------------------|-------------|

| Forecasted availability date of samples for customer                                         | 15-Mar-2007 |

| Forecasted date for <b>STMicroelectronics</b> change Qualification Plan results availability | 16-Feb-2007 |

| Estimated date of changed product first shipment                                             | 25-May-2007 |

**47/**.

| Table 3. L | ist of | Attachme | nts |

|------------|--------|----------|-----|

|------------|--------|----------|-----|

| Customer Part numbers list |  |

|----------------------------|--|

| Qualification Plan results |  |

| PCN APM-IPC/07/2330          |

|------------------------------|

| Notification Date 02/23/2007 |

| Name:                        |

| Title:                       |

| Company:                     |

| Date:                        |

| Signature:                   |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

|                              |

**A**7/.

### **DOCUMENT APPROVAL**

| Name               | Function                   |

|--------------------|----------------------------|

| Menniti, Pietro    | Division Marketing Manager |

| Borghi, Maria Rosa | Division Product Manager   |

| Motta, Antonino    | Division Q.A. Manager      |

**A7**/.

## 2ND SOURCE ASSEMBLY LINE OF PM6685xx device (UN08 line) & PM6680xx device (UN13 line) - VFQFPN 5X5X1 package - IN UTAC (ex Nseb) Thailand SUBCON

#### WHAT:

APM-IPC Div. is going to qualify a 2nd source assembly plant in UTAC (ex Nseb) Thailand subcon for the device PM6685xx (UN08 line) & PM6680xx (UN13 line) in VFQFPN 5X5X1 package.

#### WHY:

Production rationalization and B-end capacity increase

#### HOW:

according to the attached qualification report

#### WHEN:

the production will start in Q2, 2007. The relevant samples could be available in March 2007

Page 1 of 08

**Q&R Project Code:**

RR000407CT6017

## **QUALITY & RELIABILITY EVALUATION REPORT**

New Package Qualification VQFN32 5X5X1.0 \*UN13ABH-BCD5s

> **VQFN24 4X4X1.0** \*UN19 AA1 - BCD5s

PB FREE solution (Sn 100%)

UTAC (EX NSEB) THAILAND SUBCONTRACTOR

#### **Abstract:**

A qualification exercise it was done, to qualify the new VQFN32 5X5X1.0 / VQFN24 4X4X1.0 using as test vehicles \*UN13ABH and \*UN19AA1 on UTAC subcontractor manufacturing assy plant.

#### **Conclusion:**

On the basis of the already achieved positive results; IQC/ Workability & testing reports, Reliability evaluation/Construction Analysis for both PKG/lines we can issued a full qualification for all the I&PC involved lines assembled in VQFN32 5X5X1.0 / VQFN24 4X4X1.0 UTAC subcontractor manufacturing.

Note:

Products pass JEDEC <u>LEV.@3</u> 260°C

Issued by

Francesco Ventura (I&PC QA&R B-END)

Approved by

Antonino Motta (I&PC /QA&R MNG )

## Reliability test conditions and results for \*UN13ABH-BCD5s

| Test         | Test short description                  |                                                 |              |                |          |                              |

|--------------|-----------------------------------------|-------------------------------------------------|--------------|----------------|----------|------------------------------|

|              | Performed on 3# STD assy lots           |                                                 |              |                |          |                              |

|              | Method                                  | Conditions                                      | Sample /Lots | Number of lots | Duration | Results<br>Fail/SS           |

| PC           | <b>Pre-Conditionin</b>                  | g: Moisture sensitivit                          | y level 3    |                |          |                              |

|              | SAM T=0 &<br>AFTER<br>PRECOND           | 192h 30°C/60% - 3<br>reflow PBT 260°C           | 100          | #3             |          | 0/300<br>NO-<br>DELAMINATION |

| <b>E.S</b> : | Preconditioning                         | JL@3 + Pressure pot                             | t            |                |          |                              |

|              | Condtions:                              | 2atm                                            | 50           | #3             | 168hrs   | 0/150                        |

| <b>E.S</b> : | Preconditioning JI                      | <b>2</b> @3 + Thermal Cycle                     |              |                |          |                              |

|              | Conditions:Ta=-5                        | 60°C/+150°C                                     | 50           | #3             | 1000Cy   | 0/150                        |

| HTS          | High Temperature Storage                |                                                 |              | •              |          |                              |

|              | No bias                                 | Tamb=150°C                                      | 50           | #3             | 1000h    | 0/150                        |

| E.S.:        | High Temperature Storage+ Thermal Cycle |                                                 |              |                |          |                              |

|              |                                         | HTS:no<br>bias,Ta=150°C,<br>T.C.>500Cy,air      | 100          | #1             | 500h     | 0/100                        |

| H.T.R.B      | High<br>Temperature<br>Reverse Bias     | Tj=150°C;500hrs<br>Vin=38V,vcc=6V,Vb<br>oot=44V | 28           | #3             | 500h     | 0/84                         |

| ESD          | Electro Static Di                       | scharge                                         |              |                |          |                              |

|              | Charge Device<br>Model                  | +/- 1KV                                         | 5            |                |          | 0/5                          |

Page 3 of 08

#### Device construction note \*UN13ABH-BCD5s

| DIE FEATURES             |   |                       |  |  |  |

|--------------------------|---|-----------------------|--|--|--|

| Die Code                 | : | PUN13ABH              |  |  |  |

| <b>Diffusion process</b> | : | A1 BCD5/BCD5S REV.D   |  |  |  |

| Wafer diameter           | : | 6"                    |  |  |  |

| <b>Diffusion site</b>    | : | CARROLLTON            |  |  |  |

|                          |   |                       |  |  |  |

| Die size                 | : | 2310 X 2310UM         |  |  |  |

| Die Tick.                | : | $280 \pm 20 \; \mu m$ |  |  |  |

| <b>Passivation</b>       | : | USG-PSG +SION-PIX     |  |  |  |

| <b>Back finishing</b>    | : | CHROMIUM/NICKEL/GOLD  |  |  |  |

|                          |   |                       |  |  |  |

| PACKAGE FEATURES       |   |                      |  |  |

|------------------------|---|----------------------|--|--|

| Technical code(PKG)    | : | 42                   |  |  |

| Package name           | : | VFQFPN32L 5X5 X1.0   |  |  |

| Assembly site          | : | UTAC THAILAND        |  |  |

| Leadframe / substrate  | : | VFQFPN32L 5X5 2 ring |  |  |

|                        |   | Ag plating           |  |  |

| Die attach             | : | GLUE ABLEBOND 8600   |  |  |

| Wire Bonding           | : | 1.0 mils Au          |  |  |

| Solder balls / plating | : | Sn100% (Pure Tin)    |  |  |

| Assy lot               | : | NA                   |  |  |

#### Attachments:

- -Reliability tests description (MANDATORY)

- -MBD(Mont & Bond Diagram) for both line/pkg

Page 4 of 08

## Reliability test conditions and results for \*UN19ABH-BCD5s

| Test         | Test short desc                      | ription                               |              |                |          |                                 |  |  |

|--------------|--------------------------------------|---------------------------------------|--------------|----------------|----------|---------------------------------|--|--|

|              | Performed on 3# STD assy lots        |                                       |              |                |          |                                 |  |  |

|              | Method                               | Conditions                            | Sample /Lots | Number of lots | Duration | Results<br>Fail/SS              |  |  |

| PC           | Pre-Condition                        | ng: Moisture sensitivi                | ity level 3  |                |          |                                 |  |  |

|              | SAM T=0 &<br>AFTER<br>PRECOND        | 192h 30°C/60% - 3<br>reflow PBT 260°C | 100          | #1             |          | 0/100<br>NO<br>DELAMINATI<br>ON |  |  |

| <b>E.S</b> : | Preconditionin                       | Preconditioning JL@3 + Pressure pot   |              |                |          |                                 |  |  |

|              | Condtioning:                         | 2atm                                  | 50           | #1             | 168hrs   | 0/50                            |  |  |

| <b>E.S</b> : | Preconditioning JL@3 + Thermal Cycle |                                       |              |                |          |                                 |  |  |

|              | Conditions:Ta=-5                     | 0°C/+150°C                            | 50           | #1             | 1000Cy   | 0/50                            |  |  |

| HTS          | High Temperatu                       | re Storage                            |              |                |          |                                 |  |  |

|              | No bias                              | Tamb=150°C                            | 50           | #1             | 1000h    | 0/50                            |  |  |

| ESD          | Electro Static Discharge             |                                       |              |                |          |                                 |  |  |

|              | Charge Device<br>Model               | +/- 1.5KV                             | 5            |                |          | 0/5                             |  |  |

**Page 5 of 08**

#### Device construction note \*UN19AA1-BCD5s

| DIE FEATURES             |   |                       |  |  |

|--------------------------|---|-----------------------|--|--|

| Die Code                 | : | SUN19AA1              |  |  |

| <b>Diffusion process</b> | : | 20 BCD5C/BCD5S CLEAN  |  |  |

|                          |   | PROCESS 8             |  |  |

| Wafer diameter           | : | 6"                    |  |  |

| <b>Diffusion site</b>    | : | CARROLLTON            |  |  |

| Die size                 | : | 1900 X 1900UM         |  |  |

| Die Tick.                | : | $280 \pm 20 \; \mu m$ |  |  |

| Passivation              | : | TEOS+PTEOS+SiOn+PIX   |  |  |

| PACKAGE FEATURES       |   |                          |  |  |

|------------------------|---|--------------------------|--|--|

| Technical code(PKG)    | : | ND                       |  |  |

| Package name           | : | VFQFPN24L 4X4 X1.0       |  |  |

| Assembly site          | : | UTAC THAILAND            |  |  |

| Leadframe / substrate  | : | VFQFPN24L 4X4 Ag plating |  |  |

| Die attach             | : | GLUE ABLEBOND 8200T      |  |  |

|                        | • | 1.0 mils Au              |  |  |

| Wire Bonding           | : |                          |  |  |

| Solder balls / plating | : | Sn100% (Pure Tin)        |  |  |

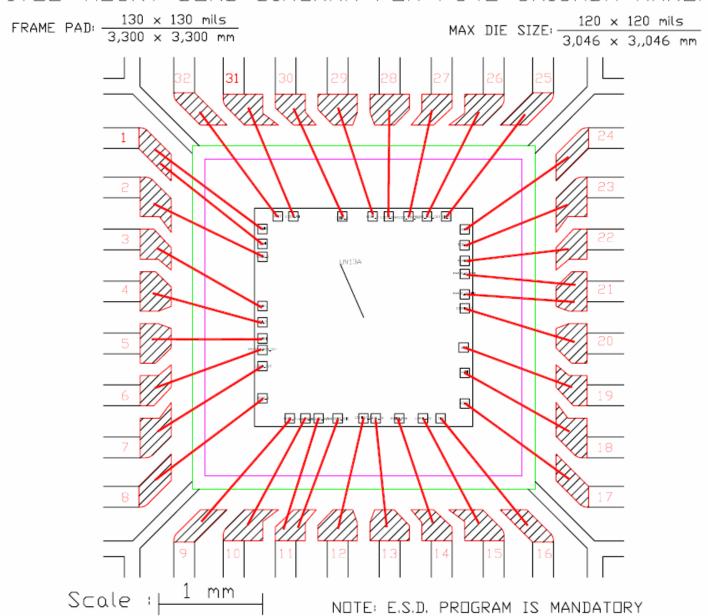

### TITLE: MOUNT BOND DIAGRAM FOR F542\*UN13ABH AMKOR

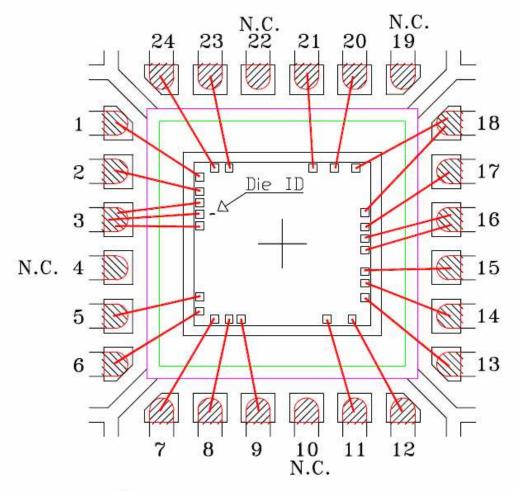

## TITLE: MOUNT AND BOND DIAGRAM FOR A5ND\*UN19AA1 NSE

FRAME PAD :  $\frac{110,24 \times 110,24 \text{ mils}}{2,800 \times 2,800 \text{ mm}}$

MAX DIE SIZE :  $\frac{100,24 \times 100,24 \text{ mls}}{2,546 \times 2,546 \text{ mm}}$

Scale : | 1 mm

E.S.D. PROGRAM IS MANDATORY

### **ATTACHMENT 1: RELIABILITY TEST DESCRIPTION**

| TEST NAME                                                               | DESCRIPTION                                                                                                                                                                                                                                                             | PURPOSE                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JLn: Jedec Level n surface mounting simulation  TCT: Temperature Cycles | The device is submitted to a typical temperature profile used for surface mounting, after a controlled moisture absorption.  The device is submitted to cycled                                                                                                          | As stand-alone test: to investigate the level of moisture sensitivity.  As preconditioning before other reliability tests: to verify that the surface mounting stress does not impact on the subsequent reliability performance.  The typical failure modes are "pop corn" effect and delamination.  To investigate failure modes related to the thermo- |

| Test                                                                    | temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                                                                                             | mechanical stress induced by the different thermal expansion of the materials interacting in the diepackage system. Typical failure modes are linked to metal displacement, dielectric cracking, moulding compound delamination, wire-bonds failure, die-attach layer degradation.                                                                       |

| PPT: Pressure Pot Test                                                  | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                                                                                                                                                | To investigate corrosion phenomena affecting die or package materials, related to chemical contamination and package hermeticity.                                                                                                                                                                                                                        |

| HTS: High Temperature Storage                                           | The device is stored in unbiased condition at the max. temperature allowed by the package materials, sometimes higher than the max. operative temperature.                                                                                                              | To investigate the failure mechanisms activated by high temperature, typically wire-bonds solder joint ageing, data retention faults, metal stress-voiding.                                                                                                                                                                                              |

| TST: Thermal Shock Test                                                 | The device is submitted to cycled thermal shocks through alternate immersion in a hot and a cold oil bath.                                                                                                                                                              | To investigate failure modes related to the thermomechanical stress induced by the different thermal expansion of the materials interacting in the diepackage system. Typical failure modes are linked to metal displacement, dielectric cracking, moulding compound delamination, wire-bonds failure, die-attach layer degradation.                     |

| HTRB: High Temperature<br>Reverse Bias Test                             | The device is stressed in static configuration, trying to satisfy as much as possible the following conditions:  -) low power dissipation;  -) max. supply voltage compatible with diffusion process and internal circuitry limitations;  -) max. junction temperature. | To maximize the electrical field across either reverse-biased junctions or dielectric layers, in order to investigate the failure modes linked to mobile contamination, oxide ageing, layout sensitivity to surface effects.                                                                                                                             |

| <b>THB:</b> Temperature Humidity Bias Test                              | The device is biased in static configuration minimizing its internal power dissipation, and stored at controlled conditions of ambient temperature and relative humidity.                                                                                               | To investigate failure mechanisms activated in the die-package environment by electrical field and wet conditions. Typical failure mechanisms are electrochemical corrosion and surface effects related to the moulding compound.                                                                                                                        |

Page 9 of 08

| E.S.D | This test is performed to verify adequate pin protection to electrostatic discharges. The flow chart is the following: | TEST CONDITIONS:  • Charge Device ModelJEDEC  STANDARD JESD22-C101-A |

|-------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| •     | <ul> <li>Initial testing @ Ta=25℃</li> <li>ESD discharging @ Ta=25℃</li> <li>Final Testing @ Ta=25℃</li> </ul>         |                                                                      |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time. without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2007 STMicroelectronics - All rights reserved.

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morroco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com