# PRODUCT/PROCESS CHANGE NOTIFICATION

PCN APM-IPC/10/5986 Notification Date 10/25/2010

Additional BCD5 Technology Ang Mo Kio 6" wafers fab (AMK6) for Linear Voltage Regulator product

### **Table 1. Change Implementation Schedule**

| Forecasted implementation date for change                                                    | 15-Jan-2011 |

|----------------------------------------------------------------------------------------------|-------------|

| Forecasted availabillity date of samples for customer                                        | 05-Nov-2010 |

| Forecasted date for <b>STMicroelectronics</b> change Qualification Plan results availability | 18-Oct-2010 |

| Estimated date of changed product first shipment                                             | 24-Jan-2011 |

### **Table 2. Change Identification**

| Product Identification (Product Family/Commercial Product) | see attached list                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type of change                                             | Waferfab additional location                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Reason for change                                          | Capacity rationalization and increase                                                                                                                                                                                                                                                                                                                                                                                                             |

| Description of the change                                  | At the aim to continuously improve our service and rationalize ST assets, we are expanding the production of BCD5 technology in Ang Mo Kio 6" facility, already qualified since 2008, and running in volumes for the last 2 years (see PCN APM-IPC/08/4269, dated December 29th 2008). So,the Linear Voltage Regulator products using the above technology, today diffused in AGRATE 8" fab (AG8), will be diffused also in Ang Mo Kio 6" (AMK6). |

| Product Line(s) and/or Part Number(s)                      | See attached                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Description of the Qualification Plan                      | See attached                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Change Product Identification                              | V6 are the digits used to identify AMK6 FAB in trace code                                                                                                                                                                                                                                                                                                                                                                                         |

| Manufacturing Location(s)                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

**47**/.

|    |     |    |      | _   | _     | _      |  |

|----|-----|----|------|-----|-------|--------|--|

| Тэ | hla | 2  | lict | ∧f  | Attac | hments |  |

|    | DIE | J. | LISL | UI. | Allau |        |  |

| Customer Part numbers list |  |

|----------------------------|--|

| Qualification Plan results |  |

| Customer Acknowledgement of Receipt                       | PCN APM-IPC/10/5986          |

|-----------------------------------------------------------|------------------------------|

| Please sign and return to STMicroelectronics Sales Office | Notification Date 10/25/2010 |

| □ Qualification Plan Denied                               | Name:                        |

| □ Qualification Plan Approved                             | Title:                       |

|                                                           | Company:                     |

| □ Change Denied                                           | Date:                        |

| □ Change Approved                                         | Signature:                   |

| Remark                                                    |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

|                                                           |                              |

**47/**.

### **DOCUMENT APPROVAL**

| Name             | Function                   |

|------------------|----------------------------|

| Riviera, Antonio | Division Marketing Manager |

| Naso, Lorenzo    | Division Product Manager   |

| Motta, Antonino  | Division Q.A. Manager      |

**A7**/.

### BCD5 PROCESS DIFFUSED IN AMK6 (6")

#### WHAT:

Following the BCD5 process qualification in AMK6 notified thru PCN APM-IPC/08/4269, dated December 29th 2008, please be informed that the Linear Voltage Regulator products using BCD5 Technology, currently manufactured in AGRATE 8" plant, will be also produced in our facilities located in Singapore Ang Mo Kio 6" plant. The affected products are listed in the attached table.

#### WHY:

To optimize ST asset utilization and enhance performance for Shareholders and Customers.

#### HOW:

Qualification will be run by extension of 2008 qualification results (see PCN APM-IPC/08/4269, dated December 29th 2008) and qualification data of product belonging to the same Division (L5973D, DC-DC Converter), run of pilot lots for the highest runner Voltage Regulator device (LD39150PTR) and comparison of electrical performance between the original and the new source (by T84, EWS data, electrical characterization data).

New source material will keep the original electrical, dimensional and thermal parameters for the affected product, maintaining unchanged the current information published on the relevant datasheets. There are no changes in the packing modes or in the standard delivery quantities either.

#### WHEN:

The availability of all product lines and the ramp up in the new location will be finalized within Q4 2010.

### Samples availability:

Samples of P/N LD39150PTR, will be available by wk46 2010. For other P/Ns, samples will be made available upon request.

### **Change implementation schedule:**

The production start and first shipments will be implemented according to our work in progress and materials availability as indicated in the schedule below:

| Product Family Code | Product Family<br>Description | 1st Shipments    |

|---------------------|-------------------------------|------------------|

| 32                  | Linear Voltage Regulator      | From Week 4 2011 |

### **Product's traceability:**

Unless otherwise stated by customer specific requirement, new parts produced in AMK 6" Singapore will be differentiated as indicated below:

| Diffusion plant       | ID | Country of origin |

|-----------------------|----|-------------------|

| AGRATE AG8 (current)  | V1 | Italy             |

| ANG MO KIO AMK6 (new) | V6 | Singapore         |

Shipments from new Wafer FAB location will be tracked on the ST Standard Label as showed below:

Manufactured under patents or patents pending Assembled in: 1234567890123456 Ü Pb-free 2nd Level Interconnect STMicroelectroni Bag seal date: dd mm yyyy MSL: 12 PBT: 260 C Category: xx ECOPACK/RoHS 1234567890123456 TYPE: 1234567890123456 Total Qty: 12345 Trace codes PPYWWLL1 WX T PPYWWLL2 WX T Marking 12345678901234567890 1234567890123 Bulk ID

Wafer FAB area code will change

from: V1 to: V6

Generic ST Standard label

# **Reliability Report**

**General Information**

**Product Line** UD73 EC6

2.5A SWITCH STEP DOWN **Product Description**

SWITCHING REGULATOR

I&PC **Product division** HSOP 8L **Package** Silicon process technology BCD5-44NP Locations

Wafer fab location ANG MO KIO

AMKOR ATP1 Assembly plant location

**PHILIPPINES**

Reliability assessment Pass

### **DOCUMENT HISTORY**

| Version | Date      | Pages | Author     | Comment           |

|---------|-----------|-------|------------|-------------------|

| 1.0     | 19-Feb-09 | 10    | M. Benzoni | Original document |

|         |           |       |            |                   |

|         |           |       |            |                   |

Issued by Reviewed by

Massimo Benzoni Alceo Paratore

Approved by

Antonino Motta

Version 1.0 Page 1/12

### **TABLE OF CONTENTS**

| 1 A        | APPLICABLE AND REFERENCE DOCUMENTS   | <i>3</i> |

|------------|--------------------------------------|----------|

| 2 R        | RELIABILITY EVALUATION overview      | 4        |

| 2.1        | Objectives                           | 4        |

| 2.2        | Conclusion                           | 4        |

| 3 D        | Device Characteristics               | <i>5</i> |

| 3.1        | Device description                   | 5        |

| 3.2        | Traceability                         | 8        |

| 4 7        | Tests results summary                | <i>9</i> |

| 4.1        | Test plan and results summary        | 9        |

| <i>5 T</i> | Tests Description & detailed results | 10       |

| 5.1        | Die oriented tests                   | 10       |

| 5.2        | Package oriented tests               | 11       |

| 5.3        | Electrical Characterization Tests    | 12       |

APM Group – I&PC Division RELIABILITY - CASTELLETTO

# **1 APPLICABLE AND REFERENCE DOCUMENTS**

| Document reference | Short description                                     |

|--------------------|-------------------------------------------------------|

| AEC-Q100           | : Stress test qualification for integrated circuits   |

| SOP 2.6.10         | : General product qualification procedure             |

| SOP 2.6.11         | : Program management fro product qualification        |

| SOP 2.6.12         | : Design criteria for product qualification           |

| SOP 2.6.14         | : Reliability requirements for product qualification  |

| SOP 2.6.19         | : Process maturity level                              |

| SOP 2.6.2          | : Process qualification and transfer management       |

| SOP 2.6.20         | : New process / New product qualification             |

| SOP 2.6.7          | : Product maturity level                              |

| SOP 2.6.9          | : Package and process maturity management in Back End |

| SOP 2.7.5          | : Automotive products definition and status           |

Version 1.0 Page 3/12

### **2 RELIABILITY EVALUATION OVERVIEW**

### 2.1 Objectives

This report contains the reliability evaluation of UD73 EC6 device diffused in ANG MO KIO and assembled in HSOP 8L in AMKOR ATP1 PHILIPPINES.

According to Reliability Qualification Plan, below is the list of the trials performed:

#### **Die Oriented Tests**

- High temperature Operating Life

- High Temperature Reverse Bias

- Temperature Humidity Bias

### Package Oriented Tests

- Preconditioning

- Temperature Cycling

- Autoclave

- High Temperature Storage Life

- Temperature Humidity Storage

### Electrical Characterization

- ESD resistance test

- LATCH-UP resistance test

### 2.2 Conclusion

Taking in account the results of the trials performed the UD73 EC6 diffused in ANG MO KIO and assembled in HSOP 8L in AMKOR ATP1 PHILIPPINES can be qualified from reliability viewpoint.

Version 1.0 Page 4/12

### **3 DEVICE CHARACTERISTICS**

### 3.1 Device description

### 3.1.1 Generalities

The L5973D is a step down monolithic power switching regulator with a minimum switch current limit of 2.5A so it is able to deliver more than 2A DC current to the load depending on the application conditions. The output voltage can be set from 1.235V to 35V.

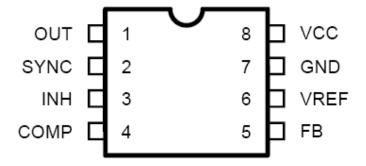

### 3.1.2 Pin connection

Version 1.0 Page 5/12

APM Group – I&PC Division RELIABILITY - CASTELLETTO

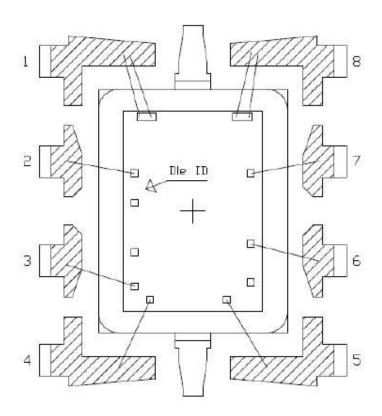

### 3.1.3 Bonding diagram

Version 1.0 Page 6/12

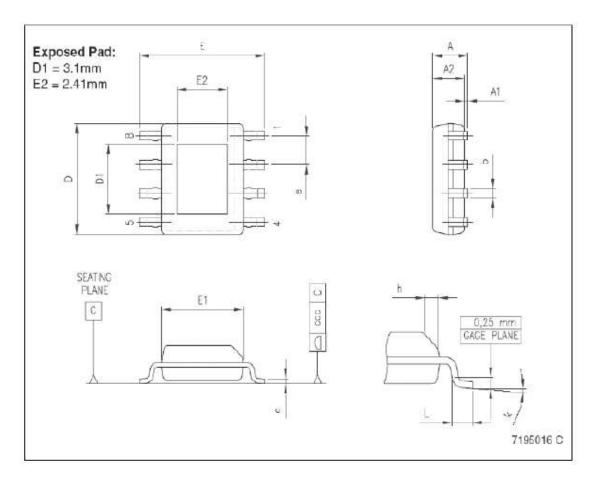

### 3.1.4 Package outline/Mechanical data

| Dina |      | mm.  |      |        | inch   |        |  |  |

|------|------|------|------|--------|--------|--------|--|--|

| Dim. | Min  | Тур  | Max  | Min    | Тур    | Max    |  |  |

| Α    |      |      | 1.70 |        | - 9    | 0.0669 |  |  |

| A1   | 0.00 |      | 0.15 |        | 0.00   | 0.0059 |  |  |

| A2   | 1.25 |      |      | 0.0492 |        |        |  |  |

| b    | 0.31 |      | 0.51 | 0.0122 |        | 0.0201 |  |  |

| С    | 0.17 |      | 0.25 | 0.0067 |        | 0.0098 |  |  |

| D    | 4.80 | 4.90 | 5.00 | 0.1890 | 0.1929 | 0.1969 |  |  |

| Е    | 5.80 | 6.00 | 6.20 | 0.2283 |        | 0.2441 |  |  |

| E1   | 3.80 | 3.90 | 4.00 | 0.1496 |        | 0.1575 |  |  |

| е    |      | 1.27 |      |        |        |        |  |  |

| h    | 0.25 |      | 0.50 | 0.0098 |        | 0.0197 |  |  |

| L    | 0.40 |      | 1.27 | 0.0157 |        | 0.0500 |  |  |

| k    | 0    |      | 8    |        |        | 0.3150 |  |  |

| CCC  |      |      | 0.10 |        |        | 0.0039 |  |  |

Version 1.0 Page 7/12

# 3.2 Traceability

| Wafer fab information            |              |  |  |  |

|----------------------------------|--------------|--|--|--|

| Wafer fab manufacturing location | ANG MO KIO   |  |  |  |

| Wafer diameter                   | 6 inches     |  |  |  |

| Wafer thickness                  | 375 μm       |  |  |  |

| Silicon process technology       | BCD5-44NP    |  |  |  |

| Die finishing back side          | Cr/Ni        |  |  |  |

| Die size                         | 2770x1980 μm |  |  |  |

| Bond pad metallization layers    | AlSiCu       |  |  |  |

| Passivation                      | SiON + PIX   |  |  |  |

| Metal levels                     | 3            |  |  |  |

| Assembly Information              |                        |  |  |

|-----------------------------------|------------------------|--|--|

| Assembly plant location           | AMKOR ATP1 PHILIPPINES |  |  |

| Package description               | HSOP8                  |  |  |

| Die pad size                      | 2.413x3.099 mm         |  |  |

| Molding compound                  | Ablebond 8290          |  |  |

| Wires bonding materials/diameters | Au/1.3 mils            |  |  |

| Die attach material               | Sumitomo G600          |  |  |

| Lead solder material              | Sn                     |  |  |

Version 1.0 Page 8/12

## **4** TESTS RESULTS SUMMARY

# 4.1 Test plan and results summary

| Die Orie | Die Oriented Tests              |                  |                 |                |          |                    |  |

|----------|---------------------------------|------------------|-----------------|----------------|----------|--------------------|--|

| Test     | Method                          | Conditions       | Sample/<br>Lots | Number of lots | Duration | Results<br>Fail/SS |  |

| HTRB     | High Temperature Reverse Bias   |                  |                 |                |          |                    |  |

|          |                                 | Tj=150℃, Vcc=40V | 77              | 3              | 1000h    | 0/231              |  |

| HTOL     | High Temperature Operating Life |                  |                 |                |          |                    |  |

|          |                                 | Tj=150℃          | 77              | 3              | 1000h    | 0/231              |  |

|          | On chip board                   | Vcc=36V, lout=2A |                 |                |          |                    |  |

| THB      | Temperature Humidity Bias       |                  |                 |                |          |                    |  |

|          |                                 | Ta=85℃, HR=85%   | 40              | 1              | 1000h    | 0/40               |  |

|          | PC Before                       | Pdut~0W, Vcc=20V |                 |                |          |                    |  |

| Package Oriented Tests |                              |                                                |                 |                |          |                    |  |

|------------------------|------------------------------|------------------------------------------------|-----------------|----------------|----------|--------------------|--|

| Test                   | Method                       | Conditions                                     | Sample/<br>Lots | Number of lots | Duration | Results<br>Fail/SS |  |

| PC                     | Pre-Conditionin              | Pre-Conditioning: Moisture sensitivity level 3 |                 |                |          |                    |  |

|                        |                              | 192h 30℃/60% - Jedec 020C                      | 200             | 1              |          | 0/200              |  |

| AC                     | Autoclave                    |                                                |                 |                |          |                    |  |

|                        | PC before                    | 121℃ 2atm                                      | 77              | 1              | 168h     | 0/77               |  |

| TC                     | Temperature Cycling          |                                                |                 |                |          |                    |  |

|                        | PC before                    | Temp. range: -50/+150℃                         | 77              | 1              | 1000cy   | 0/77               |  |

| HTSL                   | High Temperature Storage     |                                                |                 |                |          |                    |  |

|                        | No bias                      | Tamb=150℃                                      | 77              | 1              | 1000h    | 0/77               |  |

| THS                    | Temperature Humidity Storage |                                                |                 |                |          |                    |  |

|                        | No Bias                      | Tamb=85℃, RH=85%                               | 77              | 1              | 1000h    | 0/77               |  |

| Electri | Electrical Characterization Tests     |                                |                 |                |          |                    |  |

|---------|---------------------------------------|--------------------------------|-----------------|----------------|----------|--------------------|--|

| Test    | Method                                | Conditions                     | Sample/<br>Lots | Number of lots | Duration | Results<br>Fail/SS |  |

| ESD     | Electro Static Discharge              |                                |                 |                |          |                    |  |

|         | Human Body Model                      | +/- 2500V                      | 3               | 1              |          | 0/3                |  |

|         | Charge Device<br>Model                | +/- 1500V                      | 3               | 1              |          | 0/3                |  |

| LU      | Latch-Up                              |                                |                 |                |          |                    |  |

|         | Over-voltage and<br>Current Injection | Tamb=125℃<br>Jedec78 – Level B | 3               | 1              |          | 0/3                |  |

Version 1.0 Page 9/12

### 5 TESTS DESCRIPTION & DETAILED RESULTS

### 5.1 Die oriented tests

### 5.1.1 High Temperature Operating Life

This test is performed like application conditions in order to check electromigration phenomena, gate oxide weakness and other design/manufacturing defects put in evidence by internal power dissipation.

The flow chart is the following:

- Initial testing @ Ta=25℃

- Check at 168 and 500hrs @ Ta=25℃

- Final Testing @ 1000 hrs @ Ta=25℃

### 5.1.2 High Temperature Reverse Bias

This test is performed to evaluate die problems related with chip stability, layout structure, surface contamination and oxide faults.

The flow chart is the following:

- Initial testing @ Ta=25℃

- Check @ 168 and 500hrs @ Ta=25℃

- Final Testing @ 1000hrs @ Ta=25℃

### 5.1.3 Temperature Humidity Bias

The test is addressed to put in evidence problems of the die package compatibility related to phenomena activated in wet conditions such as electro-chemical corrosion.

The device is stressed is static configuration approaching some field status like power down. Temperature, Humidity and Bias are applied to the device in the following environmental conditions Ta=85 $^{\circ}$ C / RH=85 $^{\circ}$ C. Inputs pins to Low / High Voltage (alternate) to maximize voltage contrast. Test Duration 1000h

The flow chart is the following:

- Initial testing @ Ta=25℃

- Check @ 168 and 500hrs @ Ta=25℃

- Final Testing @ 1000hrs @ Ta=25℃

Version 1.0 Page 10/12

### 5.2 Package oriented tests

### 5.2.1 Pre-Conditioning

The device is submitted to a typical temperature profile used for surface mounting, after a controlled moisture absorption.

The scope is to verify that the surface mounting stress does not impact on the subsequent reliability performance. The typical failure modes are "pop corn" effect and delamination.

### 5.2.2 High Temperature Storage

The device is stored in unbiased condition at the max. temperature allowed by the package materials, sometimes higher than the max. operative temperature.

The scope is to investigate the failure mechanisms activated by high temperature, typically wire-bonds solder joint ageing, data retention faults, metal stress-voiding

### 5.2.3 Temperature Humidity Storage

The purpose of this test is to point out critical water entry path with consequent corrosion phenomena related to chemical contamination and package hermeticity.

Test flow chard is the following:

- Initial testing @ Ta=25℃.

- Readout @ 500hrs

- Final Testing @ 1000hrs @ Ta=25℃.

#### **TEST CONDITIONS:**

- Ta= 85℃

- RH= 85%

- test time= 1000 hrs

### 5.2.4 Thermal Cycles

The purpose of this test is to evaluate the thermo mechanical behavior under moderate thermal gradient stress. Test flow chart is the following:

- Initial testing @ Ta=25℃.

- Readout @ 500 cycles.

- Final Testing @ 1000 cycles @ Ta=25℃.

#### **TEST CONDITIONS:**

- Ta= -50℃ to +150℃(air)

- 15 min. at temperature extremes

- 1 min. transfer time

#### 5.2.5 Autoclave

The purpose of this test is to point out critical water entry path with consequent corrosion phenomena related to chemical contamination and package hermeticity.

Test flow chart is the following:

- Initial testing @ Ta=25℃.

- Final Testing @ 168hrs @ Ta=25℃.

#### **TEST CONDITIONS:**

- P=2.08 atm

- Ta=121℃

- test time= 168hrs

Version 1.0 Page 11/12

### **5.3 Electrical Characterization Tests**

### 5.3.1 Latch-up

This test is intended to verify the presence of bulk parasitic effects inducing latch-up.

The device is submitted to a direct current forced/sinked into the input/output pins. Removing the direct current no change in the supply current must be observed.

#### Stress applied:

| condition     | NEG. INJECTION | POS. INJECTION | OVERVOLTAGE |

|---------------|----------------|----------------|-------------|

| IN low: 0V    | -80mA          | Inom+200mA     | Vcc=46V     |

| IN high: 4.0V | -50mA          | Inom+200mA     | Vcc=46V     |

### 5.3.2 E.S.D.

This test is performed to verify adequate pin protection to electrostatic discharges. The flow chart is the following:

- Initial testing @ Ta=25℃

- ESD discharging @ Ta=25℃

- Final Testing @ Ta=25℃

#### **TEST CONDITIONS:**

O Human Body Model JEDEC STANDARD JESD22-A114

CDF-AEC-Q100-002

Charge Device Model

JEDEC STANDARD JESD22-C101

CDF-AEC-Q100-011

Version 1.0 Page 12/12

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time. without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2010 STMicroelectronics - All rights reserved.

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morroco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com